往期内容

本专栏往期内容,interrtupr子系统:

深入解析Linux内核中断管理:从IRQ描述符到irq domain的设计与实现Linux内核中IRQ Domain的结构、操作及映射机制详解中断描述符irq_desc成员详解Linux 内核中断描述符 (irq_desc) 的初始化与动态分配机制详解中断的硬件框架GIC介绍GIC寄存器介绍ARM架构中断与异常向量表机制解析深入解析GIC中断处理与内核初始化:基于Linux 4.9.88内核的详细分析GIC中断申请和中断处理流程代码解析、中断调试技巧介绍pinctrl和gpio子系统专栏:

专栏地址:pinctrl和gpio子系统

编写虚拟的GPIO控制器的驱动程序:和pinctrl的交互使用

– 末片,有专栏内容观看顺序

input子系统专栏:

专栏地址:input子系统input角度:I2C触摸屏驱动分析和编写一个简单的I2C驱动程序– 末片,有专栏内容观看顺序

I2C子系统专栏:

专栏地址:IIC子系统具体芯片的IIC控制器驱动程序分析:i2c-imx.c-CSDN博客– 末篇,有专栏内容观看顺序

总线和设备树专栏:

专栏地址:总线和设备树设备树与 Linux 内核设备驱动模型的整合-CSDN博客– 末篇,有专栏内容观看顺序

目录

往期内容1.处理流程对比1.1 下级中断控制器的类别1.1.1 链式中断控制器(chained)1.1.2 层级中断控制器(hierarchy) 1.2 链式中断控制器的处理流程1.3 层级中断控制器的处理流程1.4 处理流程对比 2.链式中断控制器驱动程序编写2.1 链式中断控制器的重要函数和结构体2.1.1 回顾处理流程2.1.2 irq_domain的核心作用 2.2 硬件模型2.3 编程 3.层级中断控制器驱动程序编写3.1 层级中断控制器的重要函数和结构体3.1.1 回顾流程3.1.2 irq_domain的核心作用 3.2 硬件模型3.3 编程

1.处理流程对比

Linux 4.9.88内核源码

Linux-4.9.88\drivers\gpio\gpio-mxc.c?gpio-mxc.cLinux-4.9.88\arch\arm\boot\dts\imx6ull.dtsi 1.1 下级中断控制器的类别

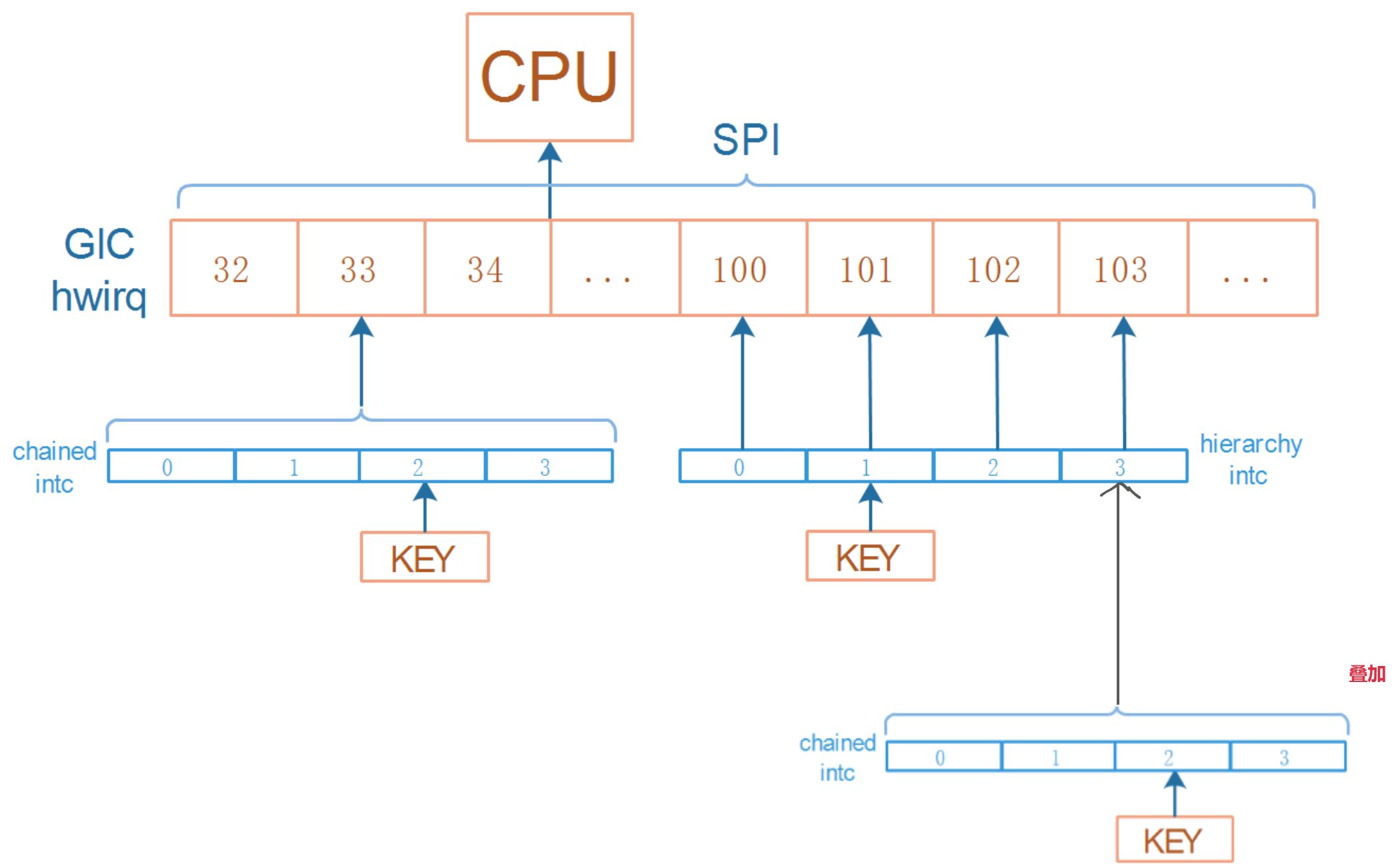

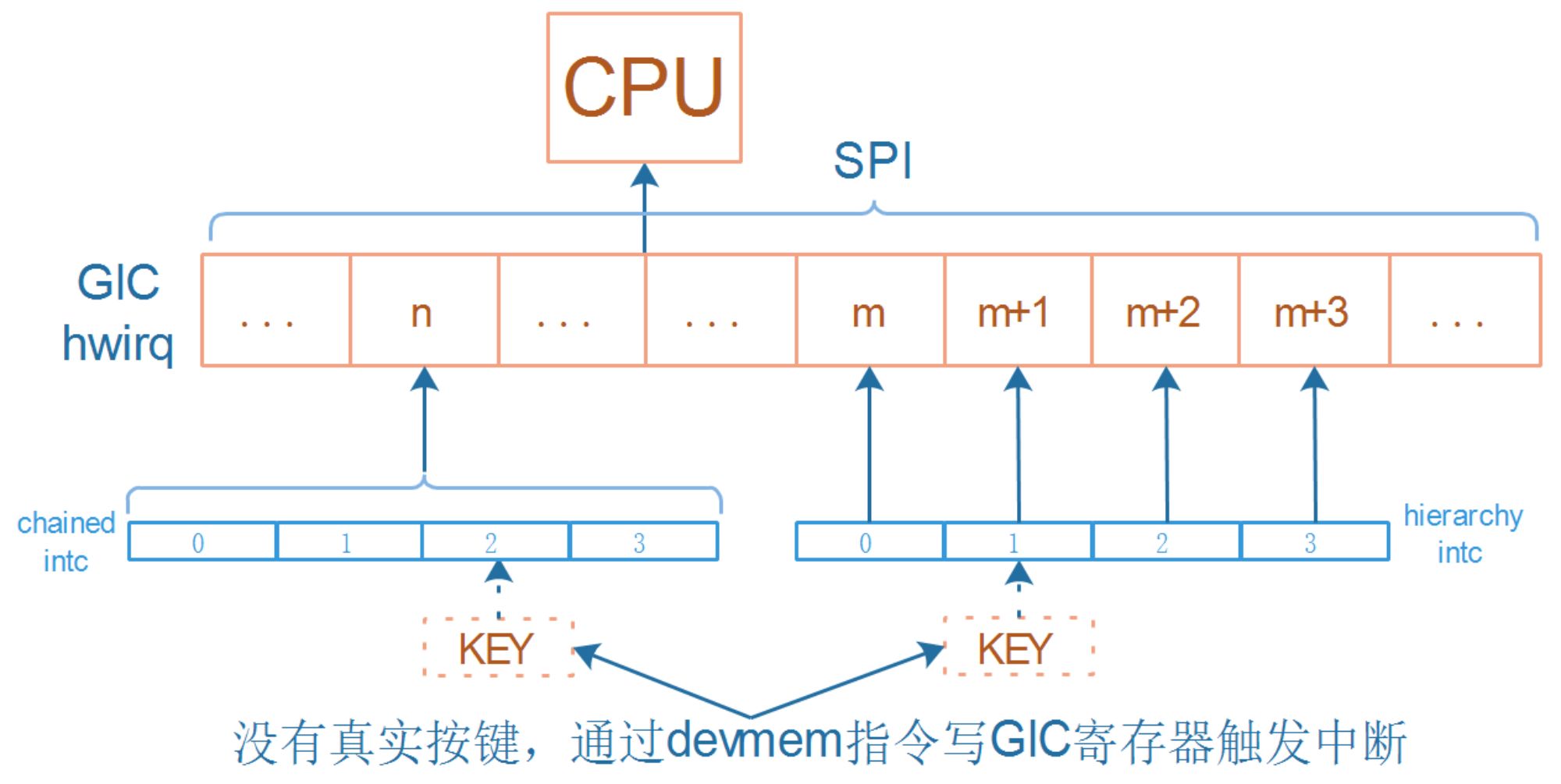

在后续课程中我们把GIC之下的中断控制器分为两类:链式(chained)、层级(hierarchy)。

(这个分类并没有官方定义)

1.1.1 链式中断控制器(chained)

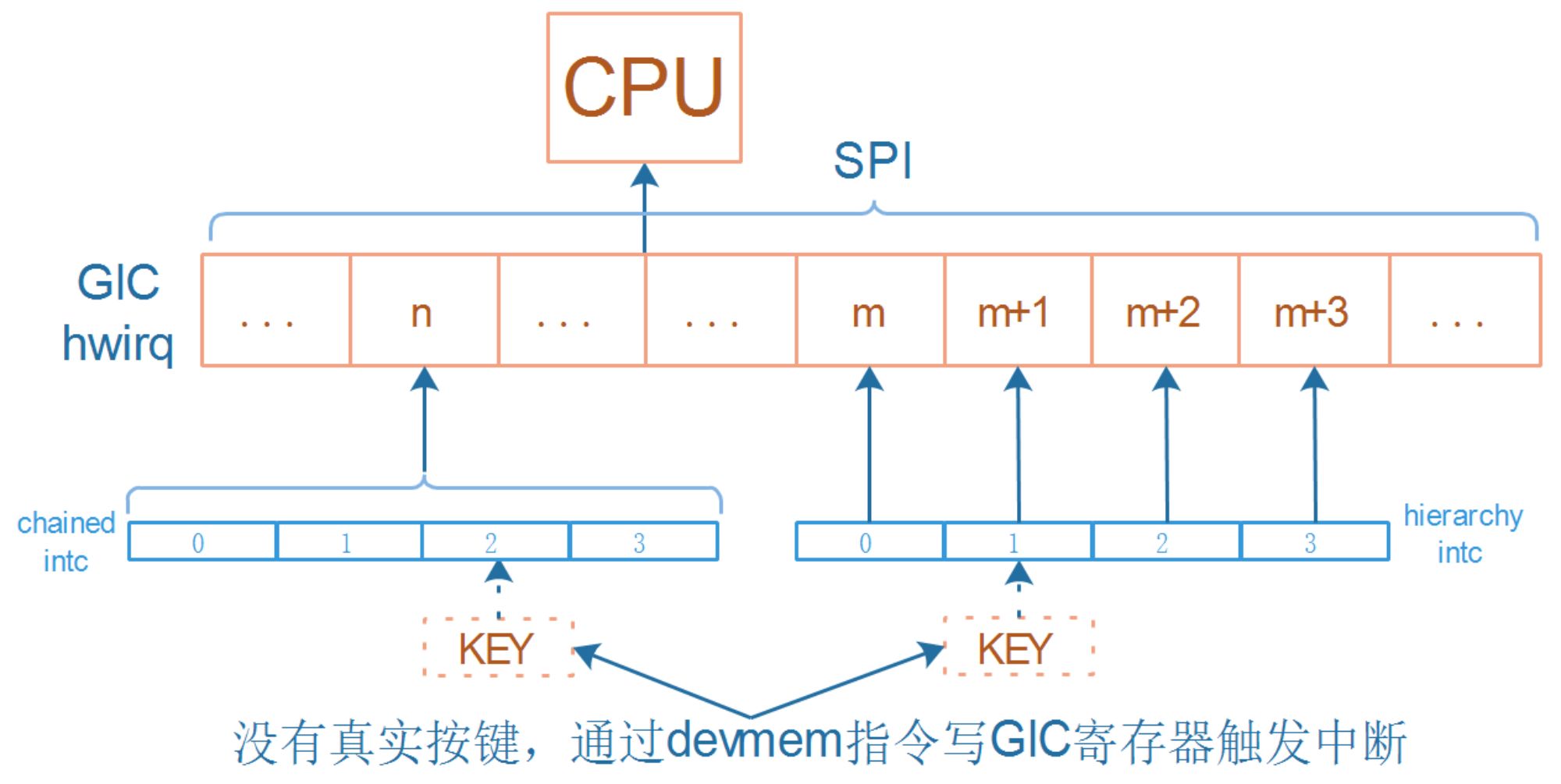

上图中,左边的"chained intc"就是链式中断控制器。

它底下的4个中断触发时,都会导致GIC的33号中断被触发。

处理中断时,需要分辨:是谁触发了GIC 33号中断?这需要读取"chained intc"中的寄存器。

1.1.2 层级中断控制器(hierarchy)

上图中,右边边的"hierarchy intc"就是层级中断控制器。

它底下的4个中断,跟GIC中的4个中断一一对应。

处理GIC 100~103号中断时,不需要读取"hierarchy intc"的寄存器来分辨是谁触发了中断。

两种类型的中断控制器是可以组合的

1.2 链式中断控制器的处理流程

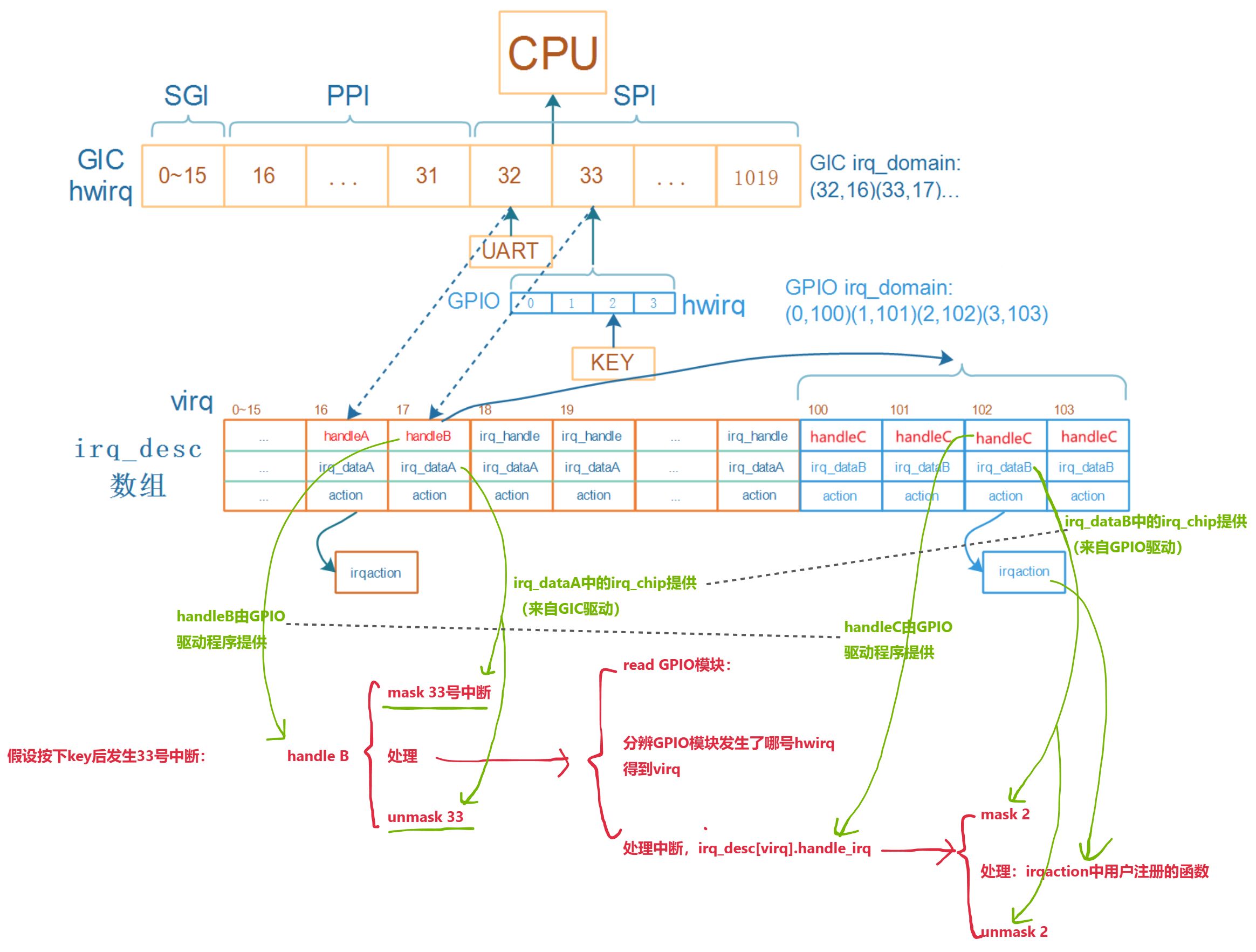

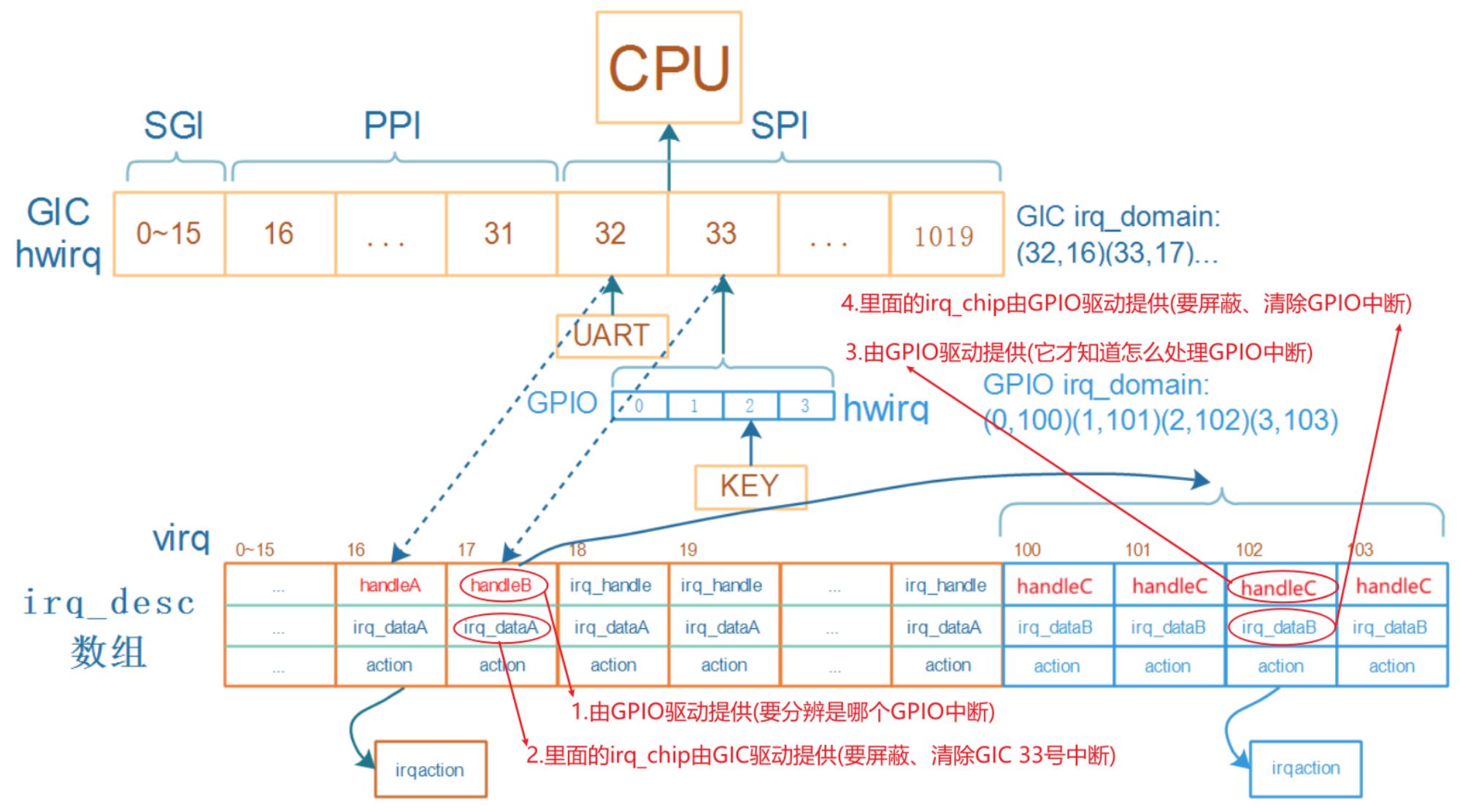

下图中:

handleA、irq_dataA由GIC驱动提供handleB、irq_dataB由GPIO驱动提供handleC也是GPIO驱动提供

假设GPIO模块下有4个引脚,都可以产生中断,都连接到GIC的33号中断

GPIO就是一个链式中断控制器,它底下有4个中断

对于GPIO模块中0~3这四个hwirq,分配四个irq_desc

可以一下子分配4个:legacy,老方法也可以用到时再分配:linear,新方法假设这4个irq_desc的序号为100~103,在GPIO domain中记录(0,100) (1,101)(2,102) (3,103)

对于KEY,注册中断时就是:request_irq(102, ...)

按下KEY时:

程序从GIC中读取寄存器知道发生了33号中断,通过GIC irq_domain可以知道virq为17

处理virq 17号中断:调用irq_desc[17].handle_irq,即handleB

mask/ack中断: 调用irq_desc[17].irq_data->irq_chip的函数,即irq_dataA

细分中断源、处理

读取GPIO寄存器,确定是GPIO里2号引脚发生中断

通过GPIO irq_domain可以知道virq为102

处理virq 102号中断:调用irq_desc[102].handle_irq,即handleC

mask/ack中断: 调用irq_desc[102].irq_data->irq_chip的函数调用irq_desc[102].action链表中用户注册的函数unmask中断: 调用irq_desc[102].irq_data->irq_chip的函数unmask中断: 调用irq_desc[17].irq_data->irq_chip的函数

1.3 层级中断控制器的处理流程

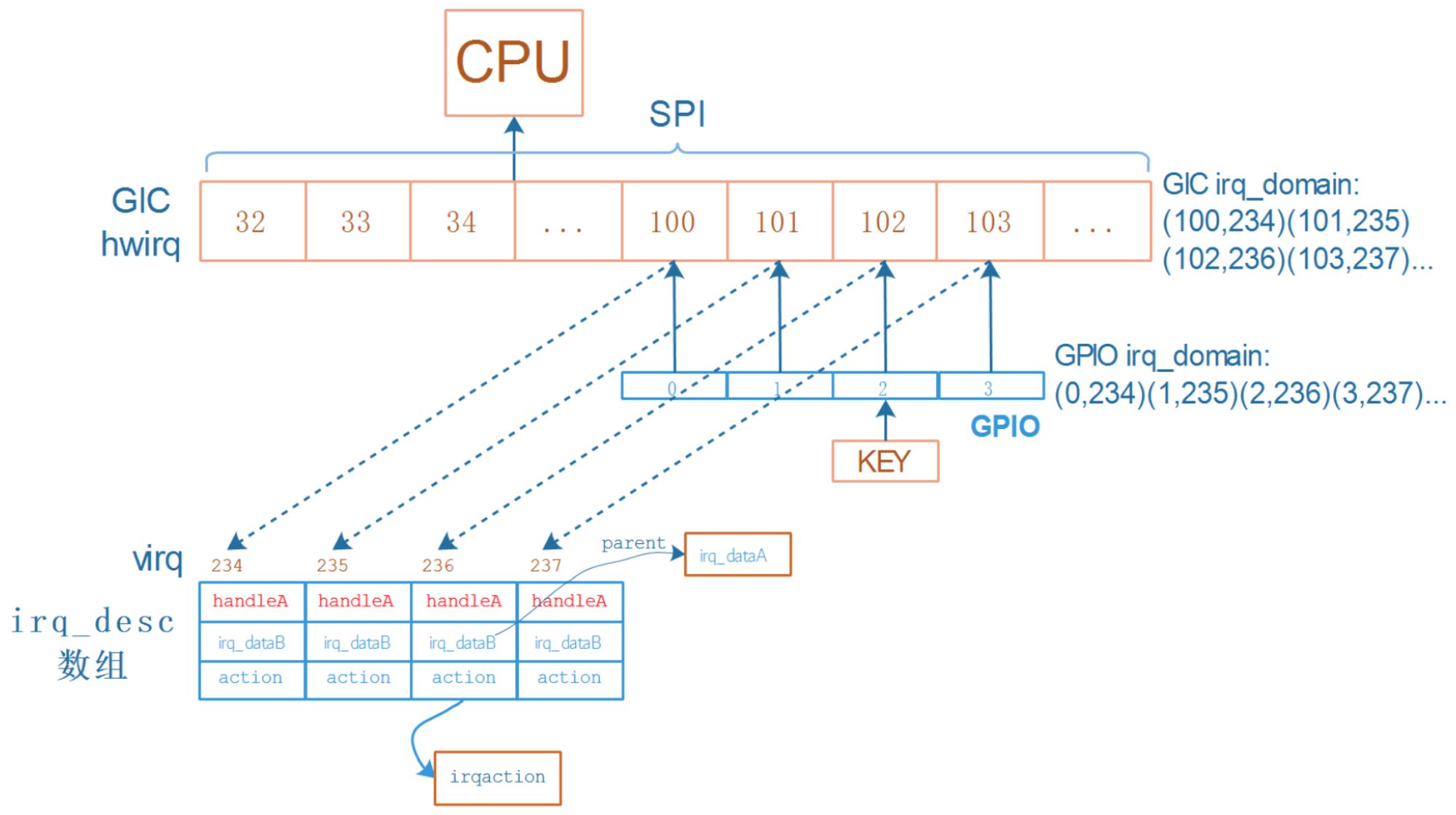

下图中:

handleA、irq_dataA由GIC驱动提供irq_dataB由GPIO驱动提供,不需要handleB

假设GPIO模块下有4个引脚,都可以产生中断,分别链接到GIC的100~103号中断

GPIO就是一个层级中断控制器

对于GPIO模块中0~3这四个hwirq,分配四个irq_desc,用到时再分配

假设这4个irq_desc的序号为234~237

在GIC domain中记录(100,234) (101,235)(102,236) (103,237)在GPIO domain中记录(0,234) (1,235)(2,236) (3,237)对于KEY,注册中断时就是:request_irq(236, ...)

按下KEY时:

程序从GIC中读取寄存器知道发生了102号中断,通过GIC irq_domain可以知道virq为236

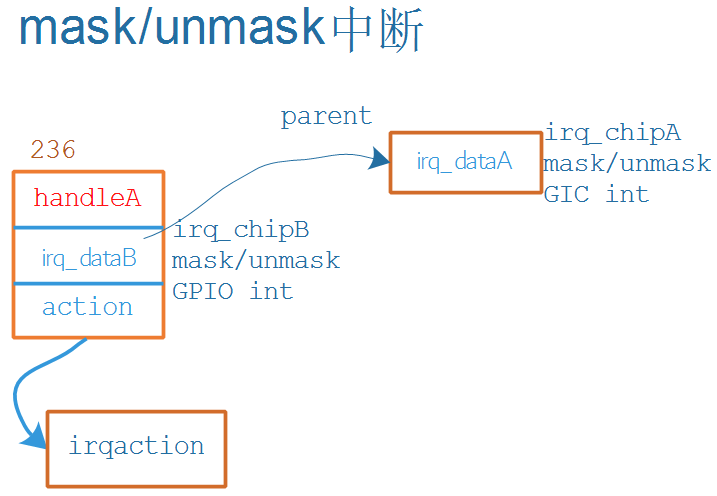

处理virq 236号中断:调用irq_desc[236].handle_irq,即handleA

mask/ack中断:

调用irq_desc[236].irq_data->irq_chip的函数,即irq_dataB

它会调用父级irq_dataA->irq_chip的函数调用irq_desc[236].action链表中用户注册的函数

unmask中断:

调用irq_desc[236].irq_data->irq_chip的函数,即irq_dataB

它会调用父级irq_dataA->irq_chip的函数1.4 处理流程对比

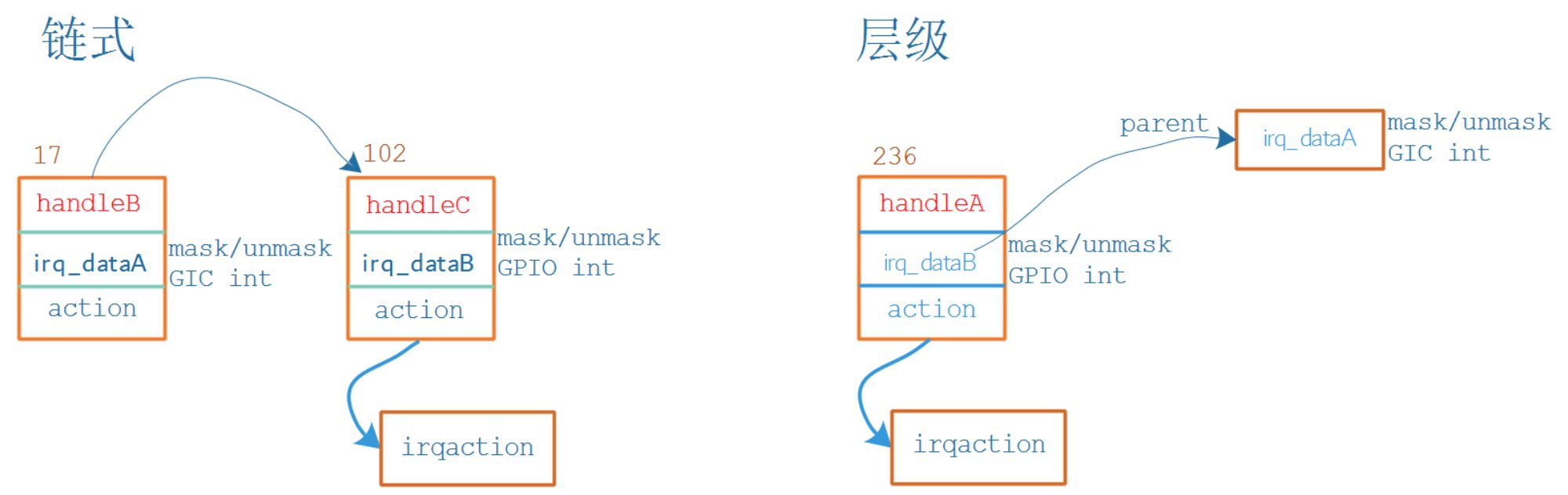

可以说:链式是mask和unmask是从上往下的,而层级是从下往上的

2.链式中断控制器驱动程序编写

Linux 4.9.88内核源码

`Linux-4.9.88\drivers\gpio\gpio-mxc.c```?gpio-mxc.cLinux-4.9.88\arch\arm\boot\dts\imx6ull.dtsi 芯片手册:?IMX6ULLRM.pdf

2.1 链式中断控制器的重要函数和结构体

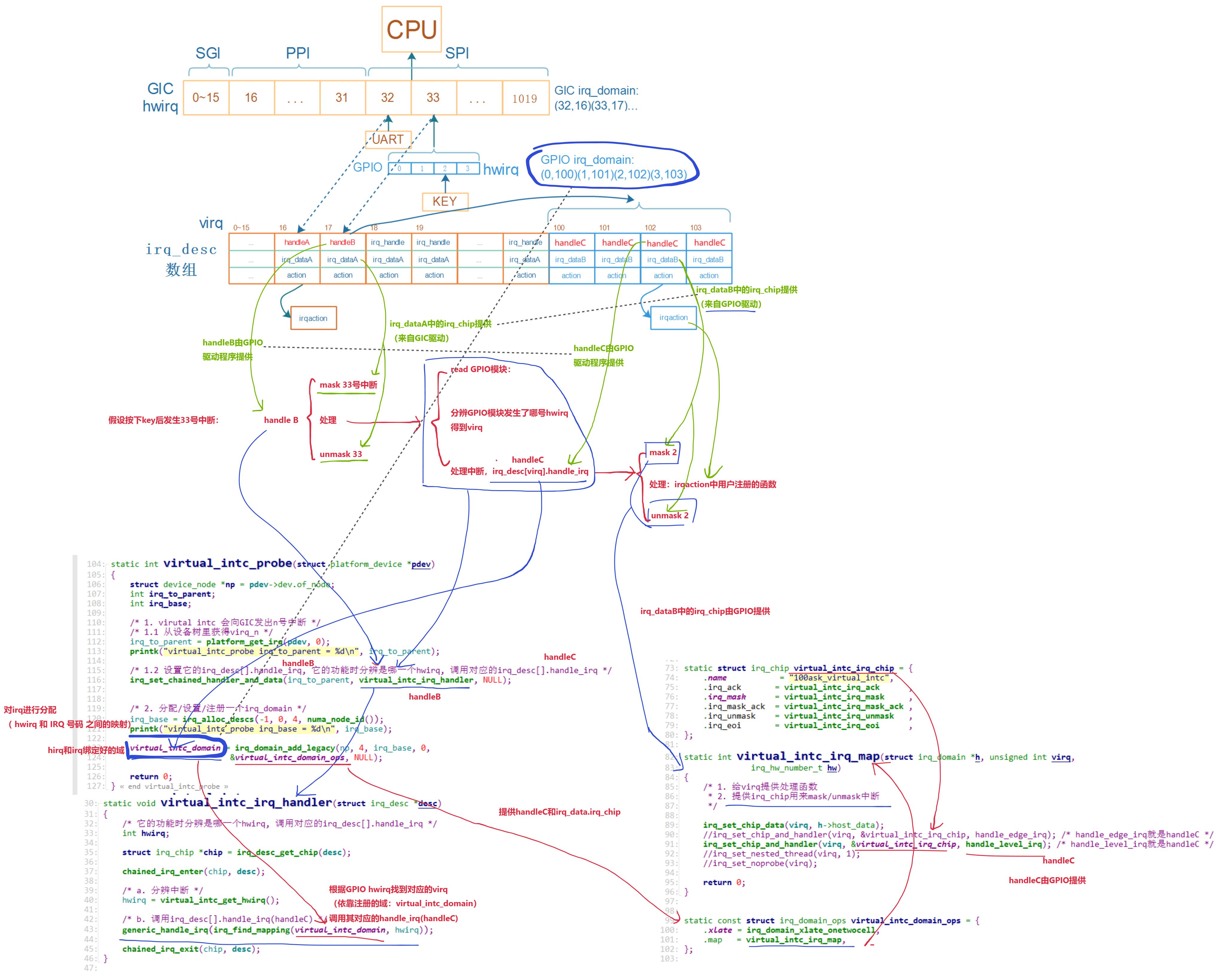

2.1.1 回顾处理流程

为方便描述,假设下级的链式中断控制器就是GPIO控制器。

沿着中断的处理流程,GIC之下的中断控制器涉及这4个重要部分:handleB、GPIO Domain、handleC、irq_chip

handleB:处理GIC 33号中断,handleB由GPIO驱动提供

屏蔽GIC 33号中断:调用irq_dataA的irq_chip的函数,irq_dataA由GIC驱动提供

细分并处理某个GPIO中断:

读取GPIO寄存器得到hwirq,通过GPIO Domain转换为virq,假设是102调用irq_desc[102].handle_irq,即handleC清除GIC 33号中断:调用irq_dataA的irq_chip的函数,由GIC驱动提供

handleC:处理GPIO 2号中断,handleC由GPIO驱动提供

屏蔽GPIO 2号中断:调用irq_dataB的irq_chip的函数,由GPIO驱动提供处理:调用actions链表中用户注册的函数清除GPIO 2号中断:调用irq_dataB的irq_chip的函数,由GPIO驱动提供2.1.2 irq_domain的核心作用

怎么把handleB、GPIO Domain、handleC、irq_chip这4个结构体组织起来,irq_domain是核心。

从使用中断的流程来讲解。

在设备树里指定使用哪个中断 gpio_keys_100ask { compatible = "100ask,gpio_key"; interrupt-parent = <&gpio5>; interrupts = <3 IRQ_TYPE_EDGE_BOTH>, };内核解析、处理设备树的中断信息

根据interrupt-parent找到驱动程序注册的irq_domain

使用irq_domain.ops中的translate或xlate函数解析设备树,得到hwirq和type

分配/找到irq_desc,得到virq

把(hwirq, virq)的关系存入irq_domain把virq存入platform_device的resource中使用irq_domain.ops中的alloc或map函数进行设置

可能是替换irq_desc[virq].handle_irq函数可能是替换irq_desc[virq].irq_data,里面有irq_chip用户的驱动程序注册中断

从platform_device的resource中得到中断号virqrequest_irq(virq, …, func)发生中断、处理中断:处理流程见上面。

2.2 硬件模型

下图中列出了链式中断控制器、层级中断控制器,只涉及左边的链式中断控制器。

内核中有各类中断控制器的驱动程序,它们涉及的硬件过于复杂,从这些杂乱的代码中去讲清楚中断体系,比较难。

实现一些虚拟的中断控制器,如下图所示。

实际板子中,可以通过按键触发中断。

对于这些虚拟的中断控制器,我们没有真实按键,通过devmem指令写GIC的PENDING寄存器触发中断。

2.3 编程

会涉及2个驱动程序:虚拟的中断控制器驱动程序,按键驱动程序,以及对应的设备树。

legacy方式:

?virtual_int_controller.c //GPIO模块

?gpio_key_drv.c //GPIO引脚

?Makefile and dts.zip

#define n 100/{ virtual_intc: virtual_intc_100ask { compatible = "XXX,virtual_intc"; interrupt-controller; #interrupt-cells = <2>; interrupt-parent = <&intc>; //interrupts = <GIC_SPI 210 IRQ_TYPE_LEVEL_HIGH>; // stm32mp157 interrupts = <GIC_SPI 122 IRQ_TYPE_LEVEL_HIGH>; // imx6ull }; gpio_keys_100ask { compatible = "XXX,gpio_key"; interrupt-parent = <&virtual_intc>; interrupts = <0 IRQ_TYPE_LEVEL_HIGH>, <1 IRQ_TYPE_LEVEL_HIGH>, <2 IRQ_TYPE_LEVEL_HIGH>, <3 IRQ_TYPE_LEVEL_HIGH>; }; };

注册irq_domain的方法:irq_domain_add_legacy(传统的)、irq_domain_add_linear(链式的)、irq_domain_add_hierarchy(层级的)

编写可以参考:gpio-mxc.c

irq_alloc_descs(irq, from, cnt, node) 提供了对irq号的分配————————————————————————————————————————————————————————————————————————————————————————————————struct irq_domain *irq_domain_add_legacy(struct device_node *of_node, unsigned int size, unsigned int first_irq, irq_hw_number_t first_hwirq, const struct irq_domain_ops *ops, void *host_data);实现irq domain的创建,且可以绑定用户已经申请的irq desc,默认irq_base被配置为正确的irq desclinear方式:

?virtual_int_controller.c

?gpio_key_drv.c

?Makefile and dts.zip

linear、legacy方式,都是用来编写链式中断控制器驱动程序,它们的关系如下表所示。

| legacy | linear | |

|---|---|---|

| 函数 | irq_domain_add_legacy | irq_domain_add_linear |

| irq_desc | 一次性分配完 | 用到再分配 |

| (hwirq,virq) | domain->linear_revmap[hwirq] = irq_data->irq; | 同左边 |

3.层级中断控制器驱动程序编写

3.1 层级中断控制器的重要函数和结构体

3.1.1 回顾流程

为方便描述,假设下级的层级中断控制器就是GPIO控制器。

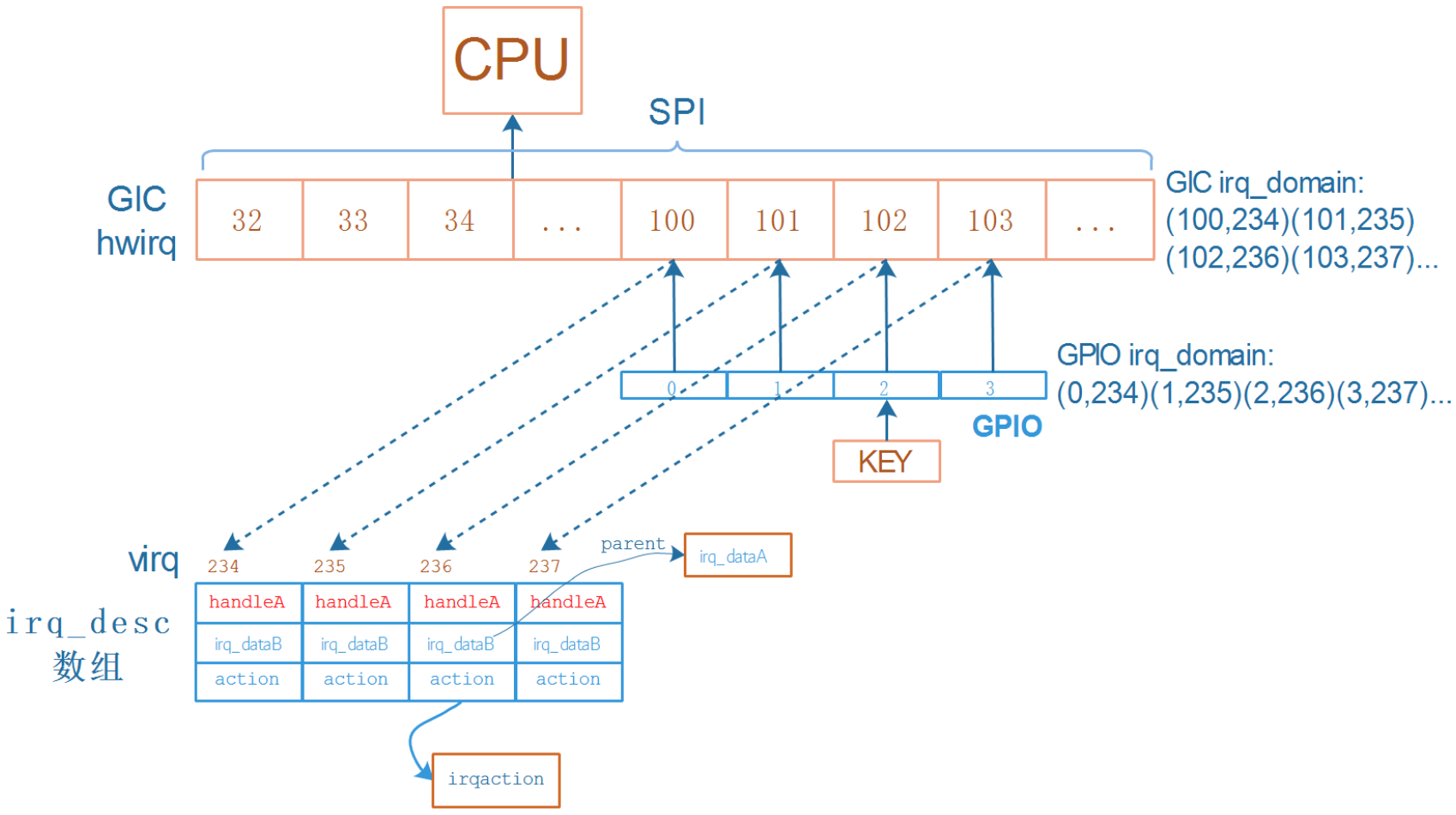

下图中:

handleA、irq_dataA由GIC驱动提供irq_dataB由GPIO驱动提供,不需要handleB

假设GPIO模块下有4个引脚,都可以产生中断,分别链接到GIC的100~103号中断

GPIO就是一个层级中断控制器

对于GPIO模块中0~3这四个hwirq,分配四个irq_desc,用到时再分配

假设这4个irq_desc的序号为234~237

在GIC domain中记录(100,234) (101,235)(102,236) (103,237)在GPIO domain中记录(0,234) (1,235)(2,236) (3,237)对于KEY,注册中断时就是:request_irq(236, ...)

按下KEY时:

程序从GIC中读取寄存器知道发生了102号中断,通过GIC irq_domain可以知道virq为236

处理virq 236号中断:调用irq_desc[236].handle_irq,即handleA

mask/ack中断:

调用irq_desc[236].irq_data->irq_chip的函数,即irq_dataB

它会调用父级irq_dataA->irq_chip的函数调用irq_desc[236].action链表中用户注册的函数

unmask中断:

调用irq_desc[236].irq_data->irq_chip的函数,即irq_dataB

它会调用父级irq_dataA->irq_chip的函数3.1.2 irq_domain的核心作用

怎么把handleA、GIC Domain和GPIO Domain、irq_chipA和irq_chipB这4个结构体组织起来,irq_domain是核心。

为方便描述,我们把上图中的层级中断控制器当做GPIO控制器。

我们从使用中断的流程来讲解。

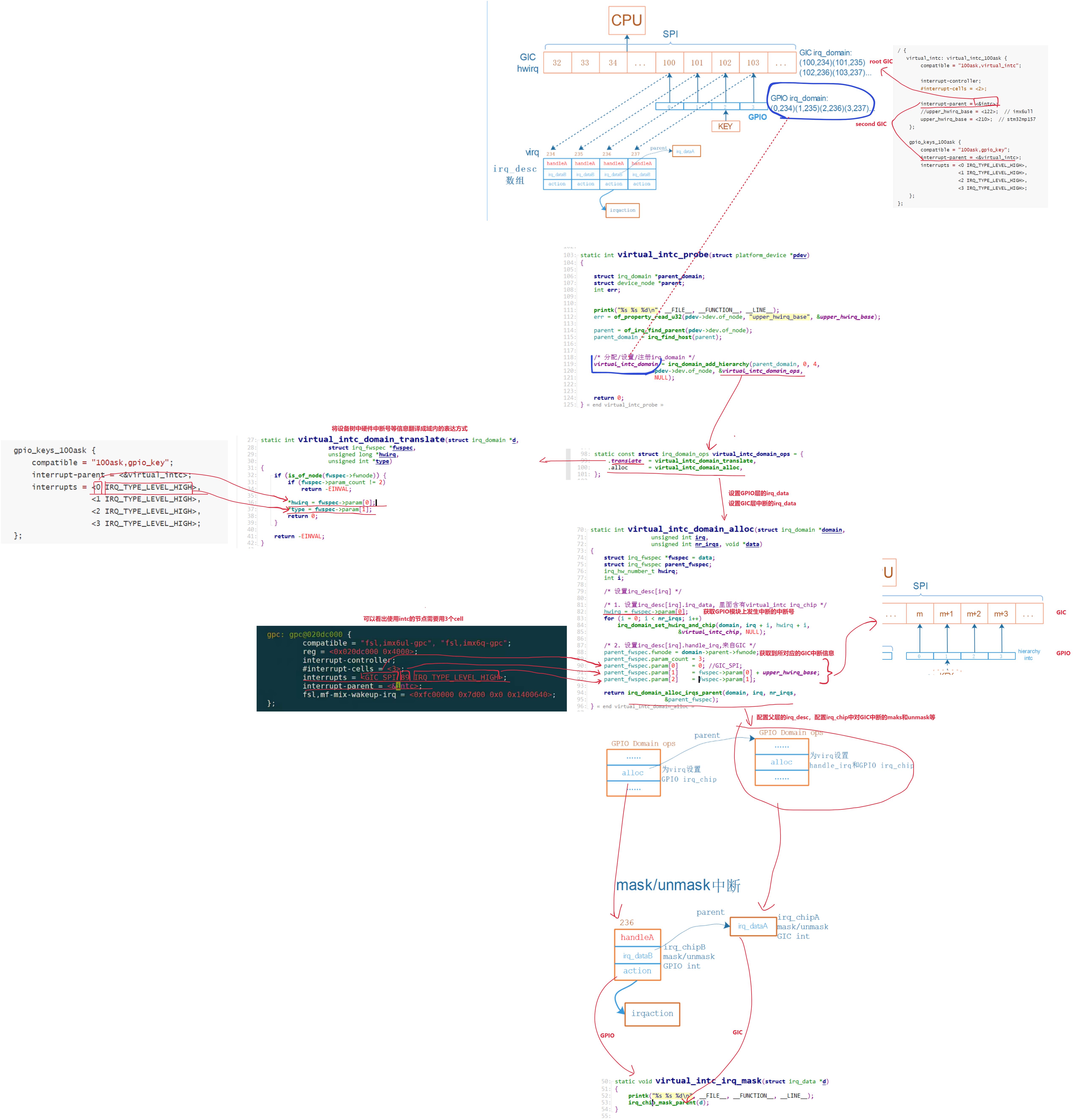

在设备树里指定使用哪个中断 gpio_keys_100ask { compatible = "XXX,gpio_key"; interrupt-parent = <&gpio5>; interrupts = <3 IRQ_TYPE_EDGE_BOTH>, };内核解析、处理设备树的中断信息

根据interrupt-parent找到驱动程序注册的GPIO irq_domain

GPIO irq_domain对设备树的解析

使用GPIO irq_domain.ops中的translate或xlate函数解析设备树,得到hwirq和type

分配/找到irq_desc,得到virq

把(hwirq, virq)的关系存入GPIO irq_domain把virq存入platform_device的resource中修改得到对应的GIC_hwirq,调用父级GIC irq_domain继续解析

把(GIC_hwirq, virq)的关系存入GIC irq_domain注意:对于同一个硬件中断,它在两个irq_domain里的virq是相同的,hwirq可能不一样。

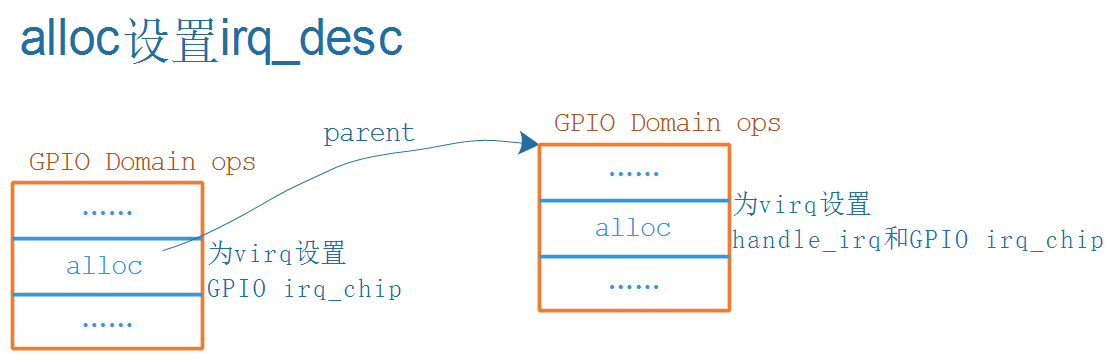

GPIO irq_domain对设备树的设置

使用GPIO irq_domain.ops中的alloc函数进行设置

替换irq_desc[virq].irq_data,里面有irq_chip改为irq_chipB,即GPIO的irq_chip

调用父级GIC irq_domain的alloc继续设置

设置irq_desc[virq].handle_irq为GIC的handle_irq,即上图中的handleA用户的驱动程序注册中断

从platform_device的resource中得到中断号virqrequest_irq(virq, …, func)发生中断、处理中断:处理流程见上面1.3。

3.2 硬件模型

下图中列出了链式中断控制器、层级中断控制器,本节课程之设计右边的层级中断控制器。

内核中有各类中断控制器的驱动程序,它们涉及的硬件过于复杂,从这些杂乱的代码中去讲清楚中断体系,比较难。

我们实现一些虚拟的中断控制器,如下图所示。

实际板子中,我们可以通过按键触发中断。

对于这些虚拟的中断控制器,我们没有真实按键,通过devmem指令写GIC的PENDING寄存器触发中断。

3.3 编程

会涉及2个驱动程序:虚拟的中断控制器驱动程序,按键驱动程序,以及对应的设备树。

虚拟的中断控制器驱动程序中,涉及2个递归处理。

alloc的递归处理

点击下载即可:

?virtual_int_controller.c

?gpio_key_drv.c

/ { virtual_intc: virtual_intc_100ask { compatible = "XXX,virtual_intc"; interrupt-controller; #interrupt-cells = <2>; interrupt-parent = <&intc>; //upper_hwirq_base = <122>; // imx6ull upper_hwirq_base = <210>; // stm32mp157 }; gpio_keys_100ask { compatible = "XXX,gpio_key"; interrupt-parent = <&virtual_intc>; interrupts = <0 IRQ_TYPE_LEVEL_HIGH>, <1 IRQ_TYPE_LEVEL_HIGH>, <2 IRQ_TYPE_LEVEL_HIGH>, <3 IRQ_TYPE_LEVEL_HIGH>; };};

irq_domain_alloc_irqs_parent 在层级化中断控制器结构中,负责将子中断控制器的中断映射到其父中断控制器,并在父中断控制器中设置相应的中断描述符(irq_desc)的处理函数(handle_irq)和中断芯片(irq_chip)。

irq_domain_alloc_irqs_parent 的作用: 当调用 irq_domain_alloc_irqs_parent 时,该函数会为子控制器的中断请求在父控制器中分配相应的中断资源,并在父控制器的 irq_desc 中设置处理函数和 irq_chip

信息。

具体来说,它会在父控制器的 irq_desc 中设置:

**handle_irq**: 用于处理该中断的具体处理函数。在发生中断时,父控制器会调用这个处理函数来响应中断。**irq_chip**: 父控制器的中断芯片信息,这决定了父控制器如何管理这个中断(例如,屏蔽、解屏蔽、确认中断等操作)。 映射关系: irq_domain_alloc_irqs_parent 会根据提供的 irq_fwspec,在父中断控制器中创建或更新硬件中断号(hwirq)和虚拟 IRQ 号(virq)之间的映射。它确保子控制器中的中断能正确地映射到父控制器的中断线,并且父控制器能够正确处理这些中断。 具体步骤:

调用 irq_domain_alloc_irqs_parent:

配置父控制器的 irq_desc:

irq_desc 结构,包括设置 handle_irq 和 irq_chip,使得父控制器知道如何处理这些来自子控制器的中断。 完成中断链路的配置:

通过这种方式,子控制器的中断能够通过父控制器进行处理,实现层级化的中断处理机制。