⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合Verilog HDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。

?文章和代码已归档至【Github仓库:hardware-tutorial】,需要的朋友们自取。或者公众号【AIShareLab】,回复 FPGA 也可获取。

文章目录

词法规定1.间隔符2.注释符3.标识符和关键词 逻辑值集合常量及其表示整数型常量实数型常量字符串常量符号常量parameter和localparam区别 数据类型(Data Types)变量的数据类型线网类型变量及其说明关于多重驱动寄存器变量类型寄存器变量类型及其说明 memory型变量的用法

词法规定

为对数字电路进行描述,Verilog语言规定了一套完整的语法结构。

1.间隔符

Verilog 的间隔符主要起分隔文本的作用,可以使文本错落有致,便于阅读与修改。间隔符包括空格符(\b)、TAB 键(\t)、换行符(\n)及换页符。

2.注释符

注释只是为了改善程序可读性,编译时不起作用。

多行注释符(用于写多行注释): /* — */;单行注释符 :以//开始到行尾结束为注释文字。3.标识符和关键词

标识符: 给对象(如模块名、电路的输入与输出端口、变量等)取名所用的字符串。以英文字母或下划线开始

如,clk、counter8、_net、bus_A 。

关键词: 用Verilog语言本身规定的特殊字符串定义语言的结构。例如,module、endmodule、input、output、wire、reg、and等都是关键词。关键词都是小写,关键词不能作为标识符使用 。

逻辑值集合

为了表示数字逻辑电路的逻辑状态,Verilog语言规定了4种基本的逻辑值。

| 0 | 逻辑0、逻辑假 |

|---|---|

| 1 | 逻辑1、逻辑真 |

| x或X | 不确定的值(未知状态) |

| z或Z | 高阻态 |

常量及其表示

三种类型的常量

整数型常量实数型常量字符串型常量整数型常量

十进制数形式的表示方法:表示有符号常量。例如:30、-2

带基数形式的表示方法:

格式为:<+/-><位宽>’<基数符号><数值>

例如:3’b101、5’o37、8’he3,8’b1001_0011

实数型常量

十进制记数法 如: 0.1、2.0、5.67

科学记数法 如: 23_5.1e2、5E-4、23510.0、0.0005

字符串常量

字符串是用双撇号括起来的字符序列,它必须包含在同一行中,不能分成多行书写。例如:

''this is a string'' ''hello world!''符号常量

Verilog 允许用参数定义语句定义一个标识符来代表一个常量,称为符号常量。定义的格式为:

parameter 参数名1=常量表达式1 ,参数名2=常量表达式2 , … 如 parameter BIT=1, BYTE=8, PI=3.14;

parameter和localparam区别

Verilog中用parameter或者localparam来定义常量,即用来定义一个标志符代表一个常量,从而提高程序的可读性。其说明格式如下:

parameter/localparam 参数名1=表达式,参数名2=表达式, …;区别:

parameter可用作在顶层模块中例化底层模块时传递参数的接口;localparam的作用域仅仅限于当前module,不能作为参数传递的接口。数据类型(Data Types)

变量的数据类型

线网型寄存器型线网类型:是指输出始终根据输入的变化而更新其值的变量,它一般指的是硬件电路中的各种物理连接.

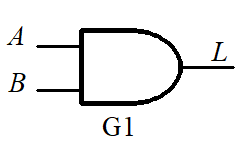

例:网络型变量L的值由与门的驱动信号A和B所决定,即L=A&B。A、B的值发生变化,线网L的值会立即跟着变化。

常用的线网类型由关键词wire定义,格式如下:

wire [n-1:0] 变量名1,变量名2,…,变量名n;线网类型变量及其说明

| 线网类型 | 功能说明 |

|---|---|

| wire, tri | 用于表示单元(元件)之间的连线,wire为一般连线; tri用于描述由多个信号源驱动的线网,并没有其他特殊 意义,两者的功能完全相同。 |

| wor, trior | 具有线或特性的线网,用于一个线网被多个信号驱动的 情况 |

| wand, triand | 具有线与特性的线网,用于一个线网被多个信号驱动的 情况 |

| trireg | 具有电荷保持特性的线网类型,用于开关级建模 |

| tri1 | 上拉电阻,用于开关级建模 |

| tri0 | 下拉电阻,用于开关级建模 |

| supply1 | 用于对电源建模,高电平1 |

| supply0 | 用于对地建模,低电平0 |

关于多重驱动

在写可综合的Verilog代码时,建议不要对同一个变量进行多次赋值(简称多重驱动),以避免出现多个信号同时驱动一个输出变量的情况。

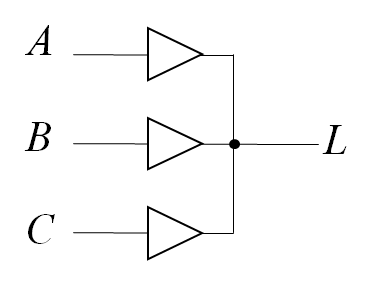

例如,A、B、C三个内部信号同时接到(驱动)一个输出端L。或者说,输出L同时被三个内部信号所驱动。此时L的逻辑值可无法确定。

寄存器型变量对应的是具有状态保持作用的电路等元件,如触发器、寄存器。寄存器型变量只能在initial或always内部被赋值。

寄存器变量类型

寄存器变量类型及其说明

| 寄存器类型 | 功能说明 |

|---|---|

| reg | 常用的寄存器型变量 |

| integer | 32位带符号的整数型变量 |

| real/realtime | 64位带符号的实数型变量 |

| time | 64位无符号的时间变量 |

reg clock; //例:一个1位寄存器变量的声明reg [3:0] counter; //例:一个4位寄存器变量的声明memory型变量的用法

Verilog通过对reg型变量建立数组来对存储器建模,可以描述RAM型存储器、ROM存储器和reg文件。数组中每个单元通过一个数组索引地址。

其格式定义如下:

reg [n-1:0] 存储器名 [m:0]注意1:

reg [N-1:0] ram; //一个N位的寄存器reg ram [N-1:0]; //一个由N个1位寄存器组成的存储器组注意2:

不可以对一个完整的寄存器组赋值,只能指定该寄存器组中的地址赋值。

公众号【AIShareLab】一起交流更多相关知识,前沿算法,Paper解读,项目源码,面经总结。