发布时间:2021/11/24

发布编号:2021-01

一、硬件平台

win10 + vivado 2020.2

芯片:xc7z100ffg900-2

二、具体流程

生成IP的流程如下:

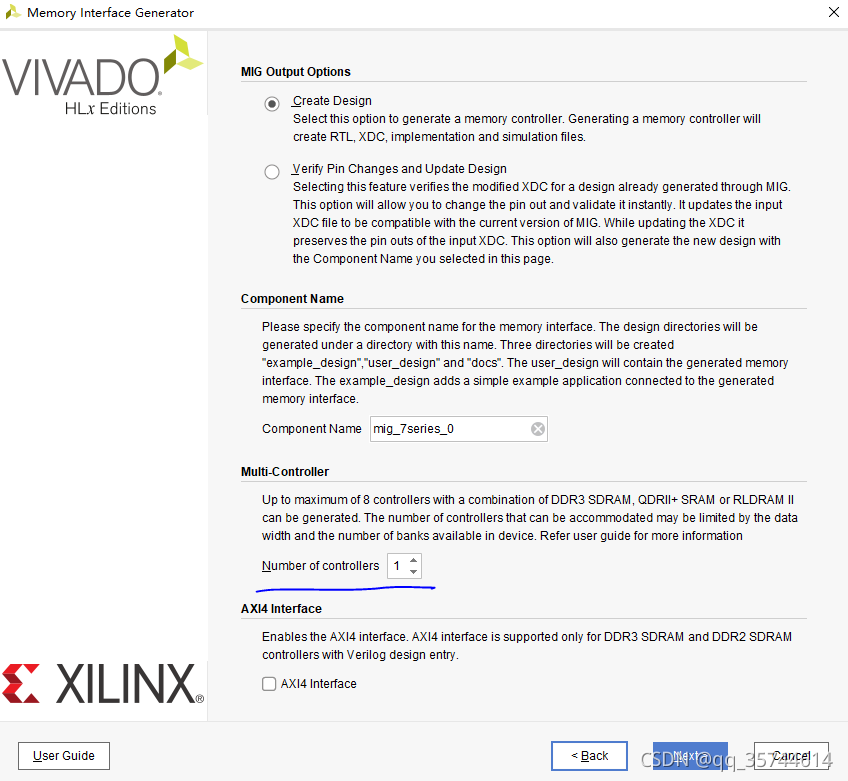

1、 选择例化IP的数量;

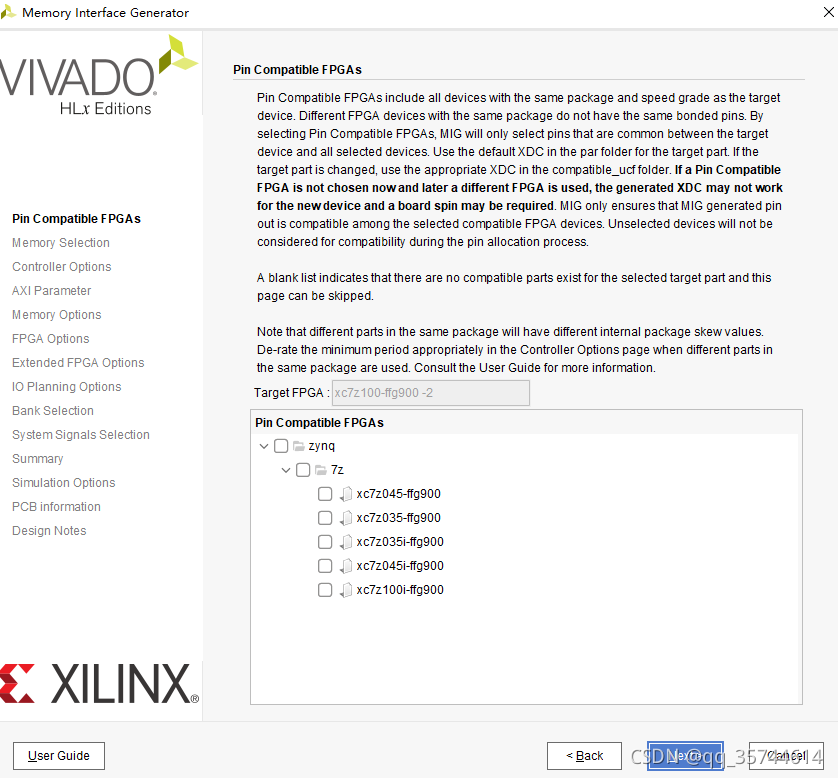

2、同类型引脚封装的FPGA型号,可以不用管;

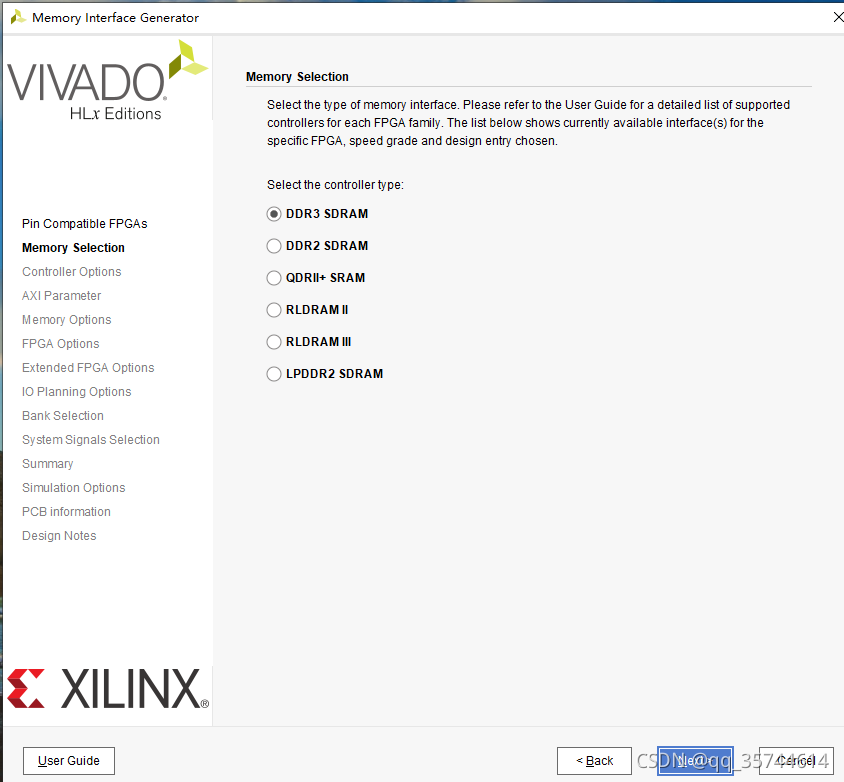

3、选择DDR3的代数

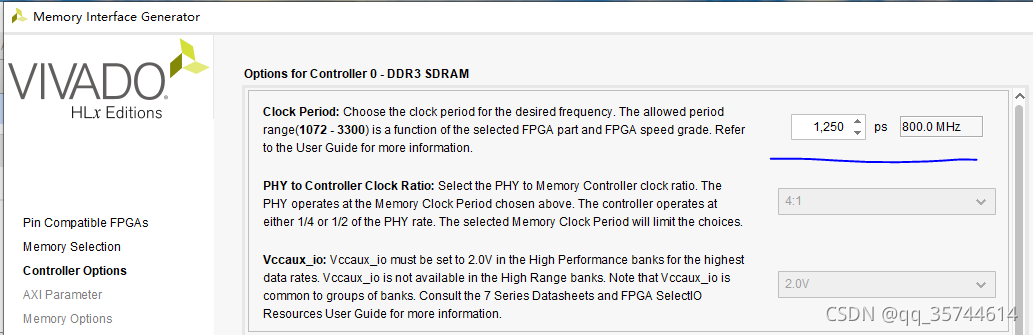

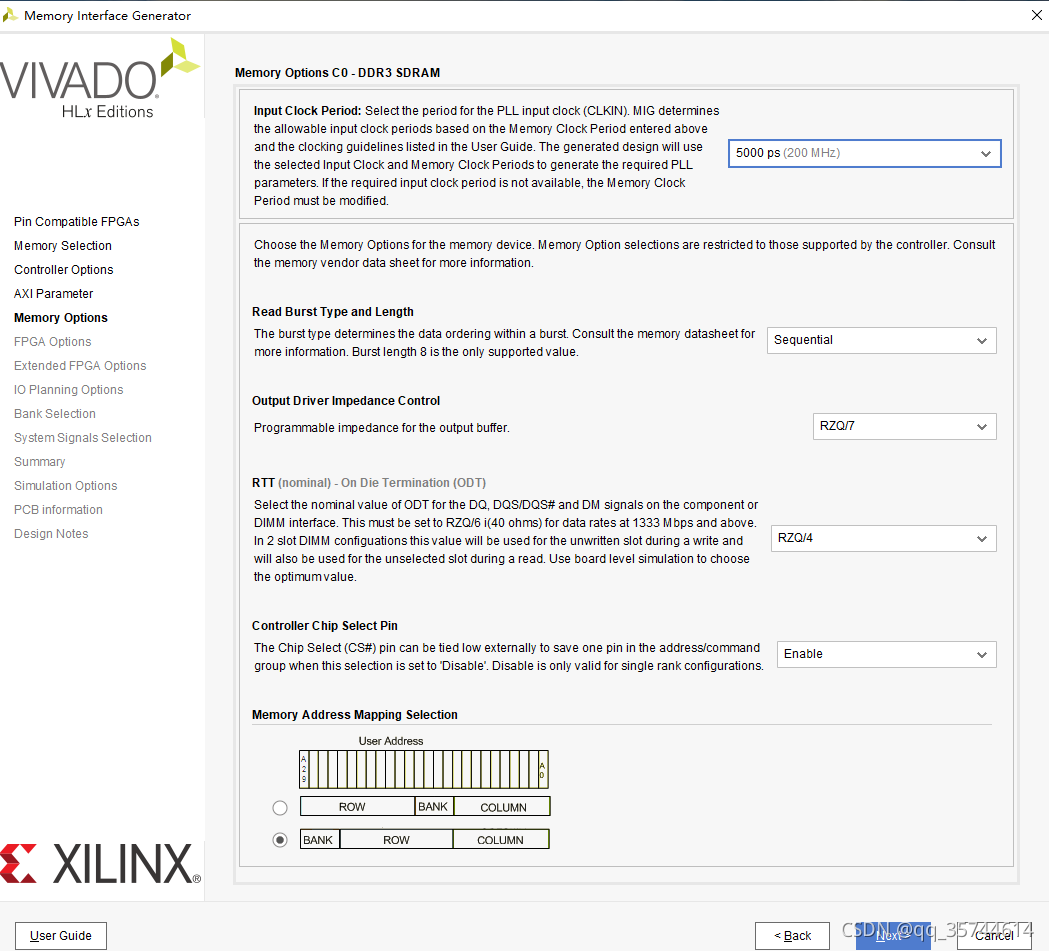

4、工作时钟800MHz,DDR3的实际工作速率就是800MHz*2(1600MHz),在工作时钟的基础上进行4:1(2:1)的分频得到用户时钟200MHz(400MHz),DDR3读写数据的时候就是用户时钟处理的,用户时钟是一定小于工作时钟的。

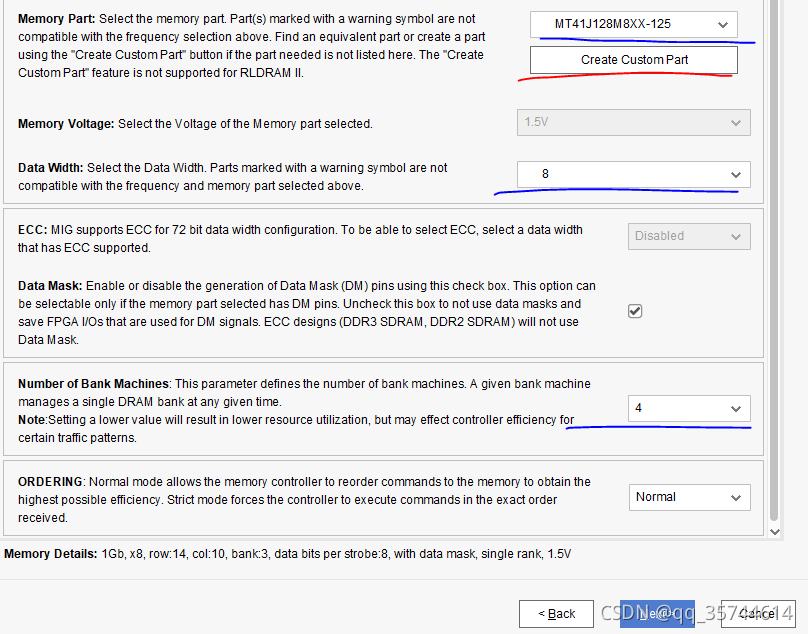

5、下面的参数就是根据实际原理图选定,红色标线的地方就是你选项中没有这个型号的时候,需要自己定义这种型号。

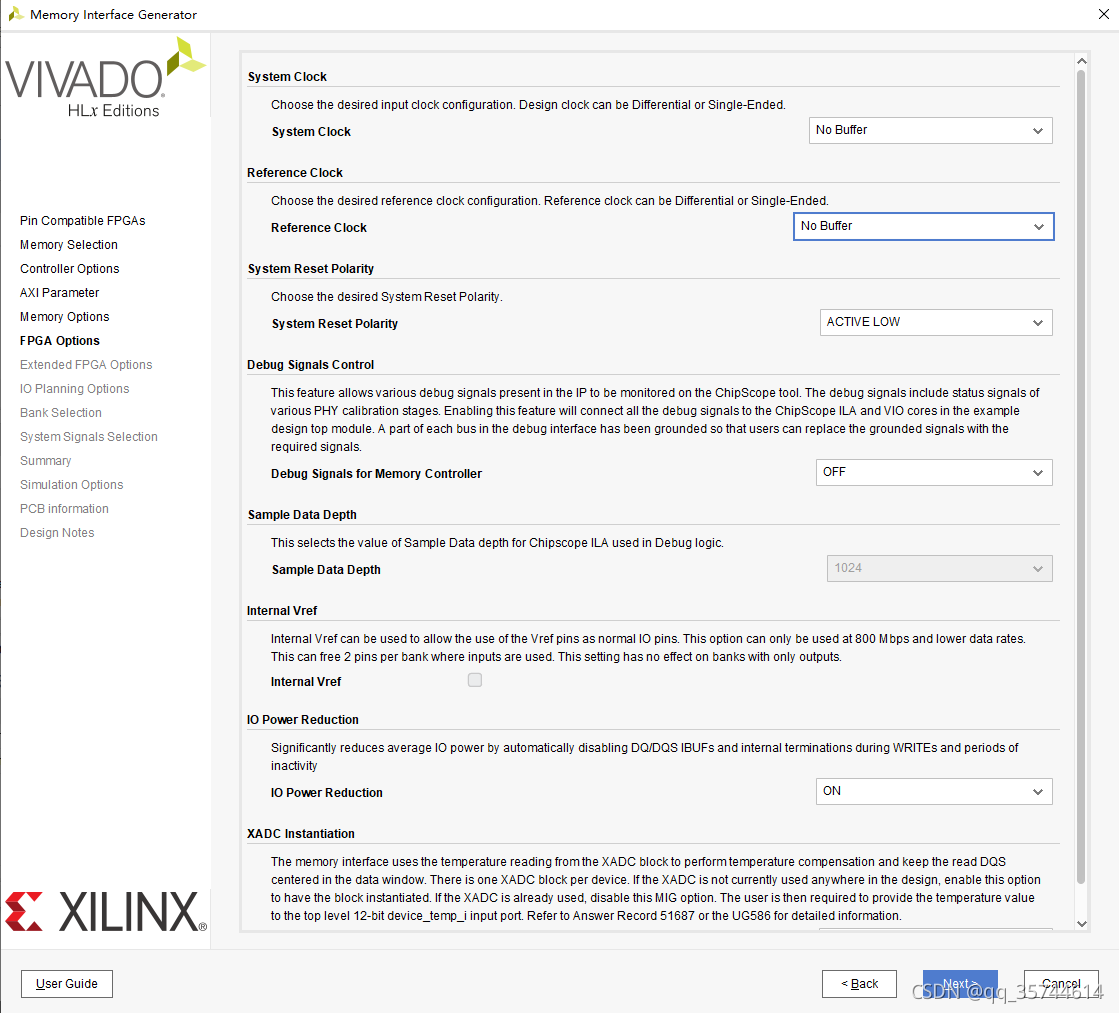

6、DDR3这个IP核输入的系统时钟和参考时钟

7、输入参考时钟和系统时钟no buffer,高复位还是低复位,这里面要注意xadc这个地方,选上会多一些xadc的几个信号。

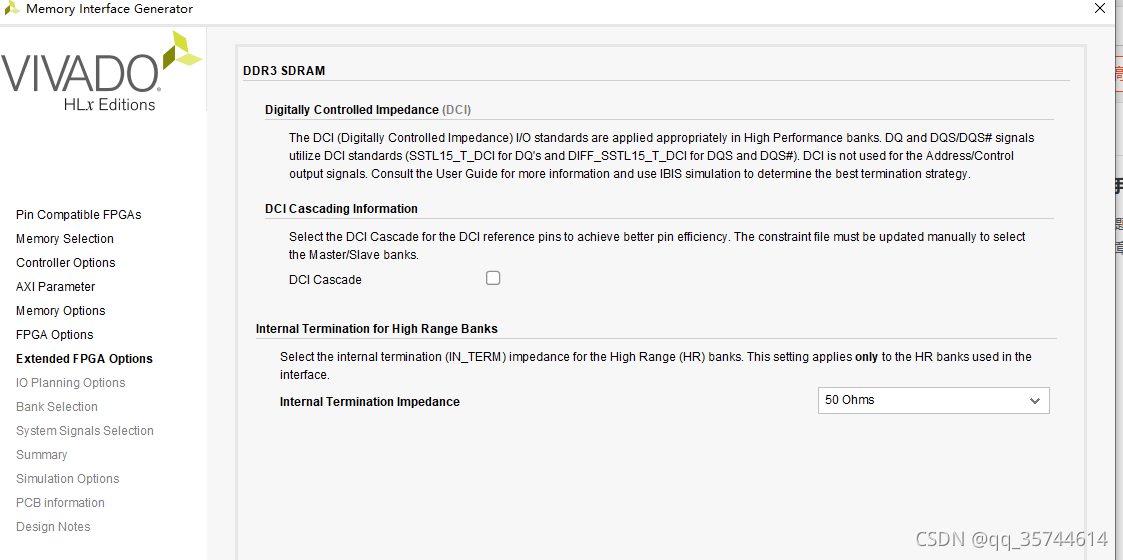

8、这步点下一步即可

9、这步点下一步即可

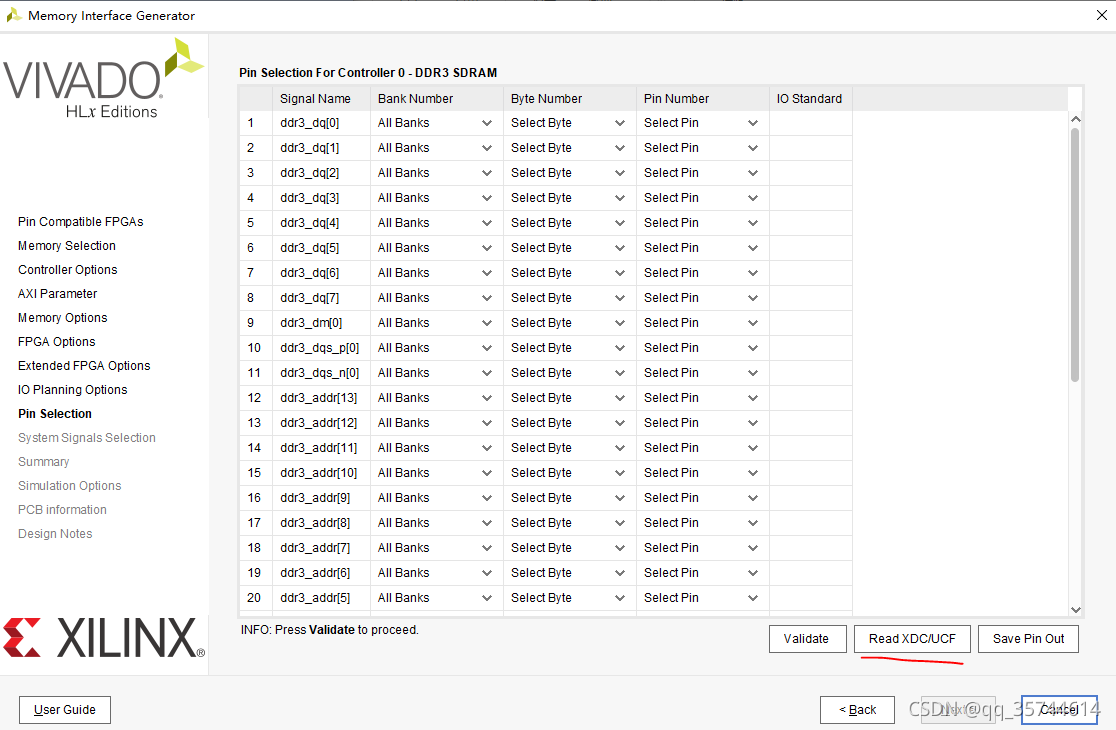

10、读取引脚约束文件(xdc/ucf)

11、下一步就是直接生成。