一个典型的PCIe总线周期

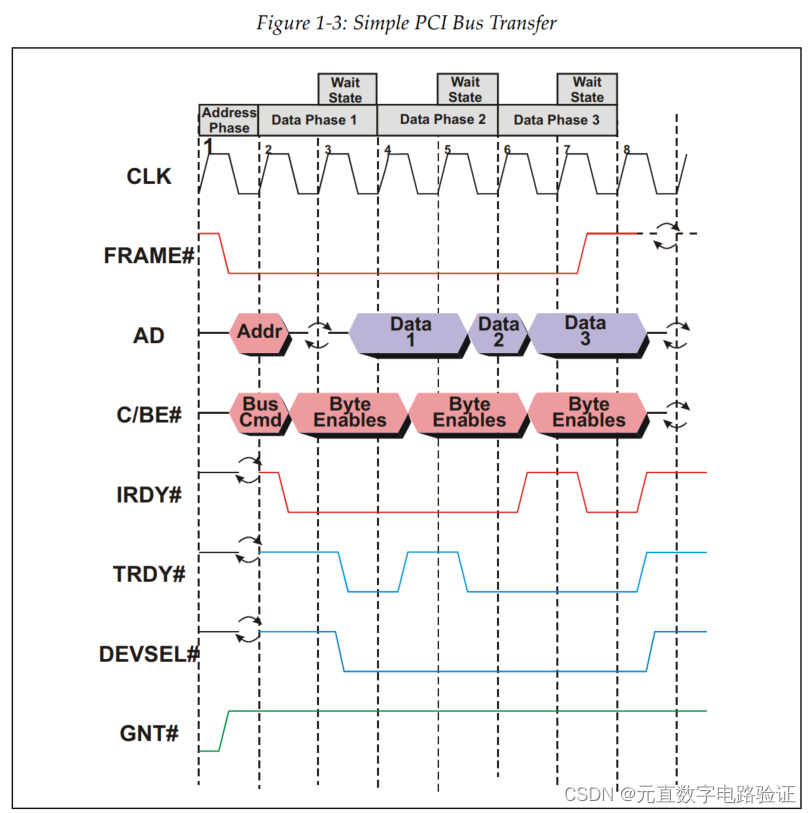

下图展示了一个典型的PCI总线周期。PCI是同步的,这意味着事件发生在时钟边缘,所以时钟显示在图表的顶部,它的上升边缘用虚线标记,因为这些是信号被输出或采样的时间。下面简要介绍一下一个总线周期的流程:

一、Typical PCI Bus Cycle

在时钟边缘1上,FRAME#(用于指示总线访问何时进行)和IRDY#(发起者准备好了数据)都是非活动的状态,表明此时总线是空闲的。与此同时,GNT#处于激活状态,这意味着总线仲裁器已经选择该设备作为下一个发起者。在时钟边缘2上,发起者断言FRAME#,表示一个新的事务已经启动。与此同时,它驱动交易的地址和指令。总线上的所有其他设备将锁定该信息,并开始解码地址的过程,以查看地址信息是否与自己匹配。在时钟边缘3上,发起者通过断言IRDY#来表明已经准备好了要传输的数据。AD总线上显示的圆形箭头符号表明,当信号所有权发生变化时,三声明总线正在经历一个循环周期(这里需要,因为这是一个读取事务;启动器驱动地址,但在相同的引脚上接收数据)。目标缓冲区没有使用关闭启动器缓冲区的同一时钟边缘来打开,因为我们希望避免两个缓冲区同时驱动一个信号的可能性,即使是很短的时间。总线上的争用可能会损坏设备,因此,取而代之的是,在打开新缓冲区之前一个时钟关闭前一个缓冲区。每个共享信号在改变方向之前都是这样处理的。在时钟边缘4上,总线上的设备已经识别出请求的地址,并通过断言DEVSEL# (设备选择)来声明该交易并参与其中。同时,它断言TRDY#(目标就绪),以表明它正在交付读数据的第一部分,并将该数据驱动到AD总线上(这可能会延迟,从断言FRAME#到TRDY#,目标允许16个时钟)。由于IRDY#和TRDY#在这里同时是活动的,数据将在时钟边缘上传输,完成第一个数据阶段。发起者知道最终将传输多少字节,但目标器不知道。该命令不提供字节计数,因此当数据阶段完成时,目标必须查看FRAME#的状态,以了解发起者对传输的数据量是否满意。如果仍然断言FRAME#,则这不是最后一个数据阶段,事务将继续使用下一个连续的字节集,就像这里的情况一样。在时钟边缘5上,目标不准备交付下一组数据,因此它取消了TRDY#。这称为插入等待状态,事务将延迟一个时钟。请求者和完成者都允许这样做,并且每个都可以将下一次数据传输延迟多达8个连续时钟。在时钟边缘6上,第二个数据项被传输,由于FRAME#仍然被断言,完成者知道请求者仍然需要更多的数据。在时钟边缘7上,发起者强制等待状态。等待状态允许设备暂停事务以快速填充或清空缓冲区,这可能很有帮助,因为它们允许事务恢复,而无需停止和重新启动。另一方面,它们的效率往往很低,因为它们不仅会使当前的交易陷入停顿,还会阻止其他设备在总线陷入停顿时访问总线。在时钟边沿8上,第三个数据集被传输,现在FRAME# 被取消断言,因此完成者可以判断这是最后一个数据项。 因此,在这个时钟之后,所有的控制线都会关闭,总线再次进入空闲状态。为了与 PCI 的低成本设计目标保持一致,同时为了减少引脚数,总线上的一些信号具有多个含义。 32位地址和数据信号被多路复用并且 C/BE#(命令/字节启用)信号共享它们的四个引脚出于相同的原因。 尽管减少引脚数是可取的,但也是 PCI 使用“周转周期”的原因,这会增加更多延迟。 它还排除了管道交易的选项(发送地址为下一个周期,同时传递前一个周期的数据)。 握手信号,例如FRAME#、DEVSEL#、TRDY#、IRDY# 和STOP# 在交易期间控制事件的时序。

二、Example PCIe Topology

2.1 Topology Characteristics

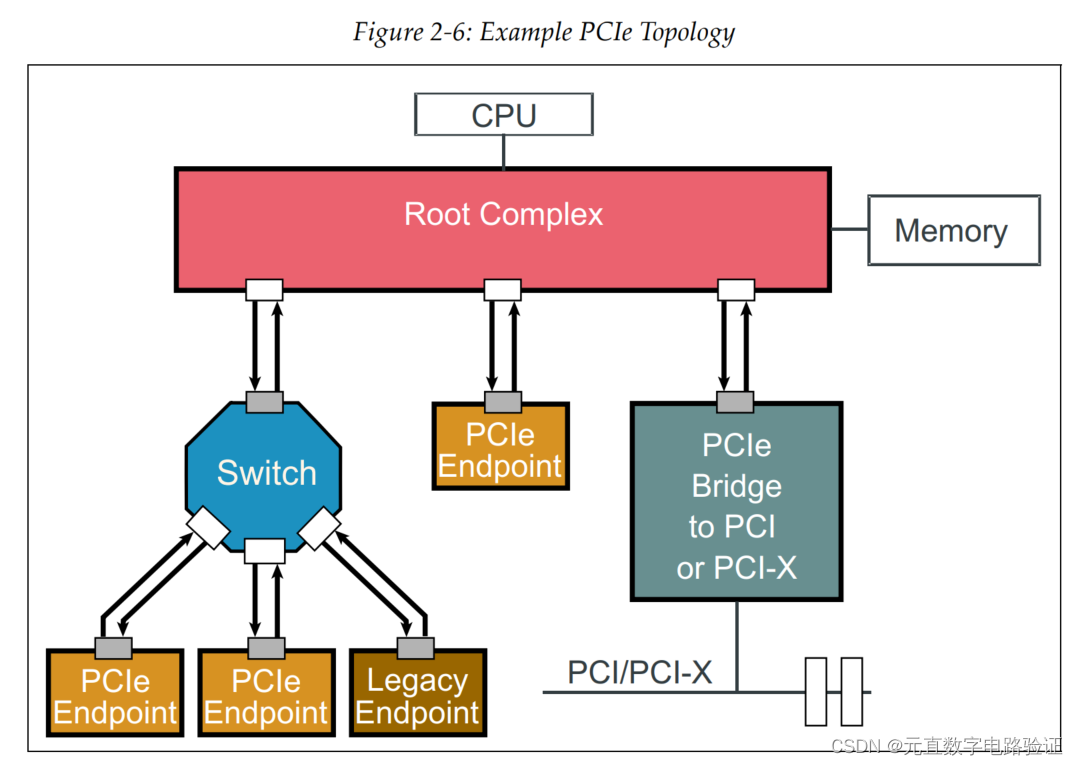

下图的顶部是一个CPU。这里要说明的一点是,CPU被认为是PCIe层次结构的顶部。就像PCI一样,PCIe只允许简单的树结构,这意味着不允许循环或其他复杂的拓扑结构。这样做是为了保持与PCI软件的向后兼容性,PCI软件使用简单的配置方案跟踪拓扑,不支持复杂的环境。

为了保持兼容性,软件必须能够以与以前相同的方式生成配置周期,并且总线拓扑结构必须与以前相同。因此,寄存器软件期望找到的所有配置仍然在那里,并以相同的方式运行。在我们有机会定义更多的术语之后,我们将稍后再回来讨论这个问题。

2.2 Root Complex

CPU和PCIe总线之间的接口可能包含多个组件(处理器接口、DRAM接口等),甚至可能包含多个芯片。总的来说,这个组被称为根复合体(RC或根)。RC驻留在PCI倒树拓扑结构的根部,并代表CPU与系统的其他部分通信。但是规范并没有完全定义它,而是给出了一个必需的和可选的功能列表。广义上,“Root Complex”可以理解为系统CPU和PCIe拓扑之间的接口,在配置空间中“PCIe Ports”被标记为“Root Ports”。

2.3 Switches and Bridges

交换机提供扇出或聚合功能并允许更多设备连接到单个 PCIe 端口。 它们充当数据包路由器并识别给定数据包需要根据其地址或其他路由选择哪条路径信息。

桥接器为其他总线提供接口,例如 PCI 或 PCI-X,甚至另一个 PCIe 总线。 “示例 PCIe 拓扑”中显示的网桥第 47 页有时称为“前向桥”,允许使用较旧的 PCI 或 PCI-将 X 卡插入新系统。 相反的类型或“反向桥”允许将新的 PCIe 卡插入旧的 PCI 系统。

2.4 Native PCIe Endpoints and Legacy PCIe Endpoints

端点是 PCIe 拓扑中的设备,它们不是交换机或桥接器,并且充当总线上交易的发起者和完成者。他们位于树形拓扑的分支的底部,并且只实现一个上游端口(面向根)。相比之下,Switch 可能具有多个下游端口,但只能有一个上游端口。设备设计用于操作较旧的总线,如 PCI-X,但现在有一个 PCIe接口在配置中将自己指定为“传统 PCIe 端点”注册并且这个拓扑包括一个。他们利用亲的东西在较新的 PCIe 设计中受到限制,例如 IO 空间和对 IO 事务的支持或锁定请求。相比之下,“本机 PCIe 端点”将是 PCIe设备从头开始设计,与向旧 PCI 添加 PCIe 接口相反设备设计。本机 PCIe 端点设备是内存映射设备(MMIO 设备)。

2.5 Software Compatibility Characteristics

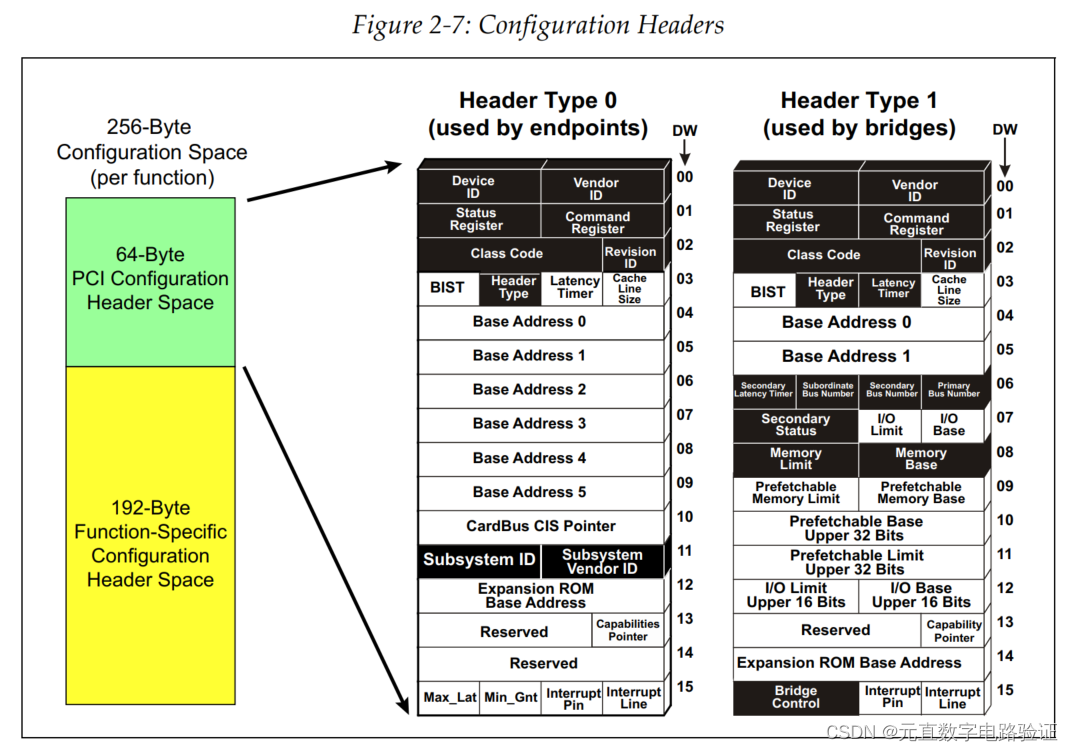

保持与旧软件兼容的一种方法是,如第50页图2-7所示,端点和桥的配置头与PCI相同。现在的一个不同之处在于桥通常被聚合到交换机和根中,但是遗留软件没有意识到这一区别,并且仍然简单地将它们视为桥。在这里,我们只是想熟悉概念,所以这里不讨论寄存器的细节。